#### Announcements

## Midterm Exam Two is scheduled on April 6 in class.

## On March 25 I will help you prepare Midterm Exam Two.

# • On March 9 I will teach "Introduction to Pipelining".

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Pearson Education, Inc.

Chapter 5 1

# **Chapter 3: Part 3 Arithmetic Functions**

- Iterative combinational circuits

- Binary adders

- Half and full adders

- Ripple carry and carry lookahead adders

- Binary subtraction

- Binary adder-subtractors

- Signed binary numbers

- Signed binary addition and subtraction

- Overflow

#### Binary multiplication

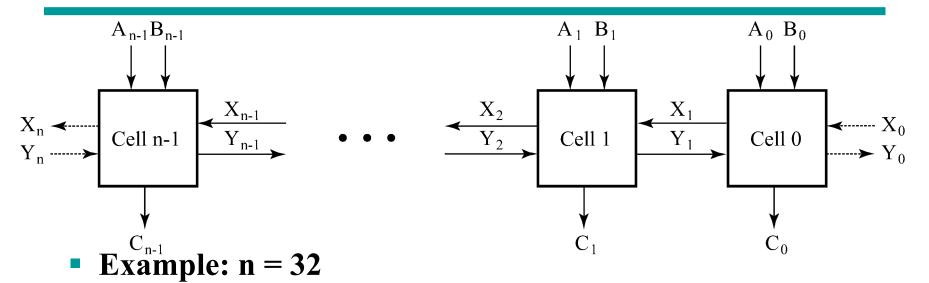

## **Iterative Combinational Circuits**

#### Arithmetic functions

- Operate on binary vectors

- Use the same subfunction in each bit position

- Can design functional block for subfunction and repeat to obtain functional block for overall function

#### Cell - subfunction block

Iterative array - a array of interconnected cells

## **Block Diagram of a 1D Iterative Array**

- Number of inputs = ?

- Truth table rows = ?

- Equations with up to ? input variables

- Equations with huge number of terms

- Design impractical!

- Iterative array takes advantage of the regularity to make design feasible

Logic and Computer Design Fundamentals PowerPoint® Slides © 2004 Pearson Education, Inc.

## **Functional Blocks: Addition**

- Binary addition used frequently

- Addition Development:

- *Half-Adder* (HA), a 2-input bit-wise addition functional block,

- *Full-Adder* (FA), a 3-input bit-wise addition functional block,

- *Ripple Carry Adder*, an iterative array to perform <u>binary addition</u>, and

- *Carry-Look-Ahead Adder* (CLA), a hierarchical structure to improve performance.

#### **Functional Block: Half-Adder**

• A 2-input, 1-bit width binary adder that performs the following computations:

| X   | 0   | 0  | 1   | 1   |

|-----|-----|----|-----|-----|

| + Y | + 0 | +1 | + 0 | + 1 |

| C S | 0 0 | 01 | 01  | 10  |

- A half adder adds two bits to produce a two-bit sum

- The sum is expressed as a <u>sum bit</u>, S and a <u>carry bit</u>, C

- The half adder can be specified as a truth table for S and C ⇒

| X | Y | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

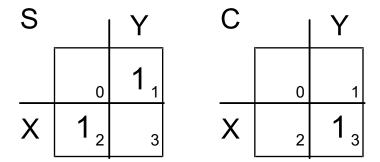

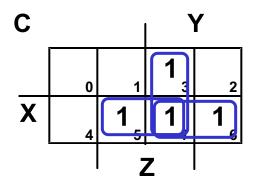

#### **Logic Simplification: Half-Adder**

- The K-Map for S, C is:

- This is a pretty trivial map! By inspection:

$$S = X \cdot \overline{Y} + \overline{X} \cdot Y = X \oplus Y$$

$$S = (X + Y) \cdot \overline{(X + Y)}$$

and

$$\mathbf{C} = \mathbf{X} \cdot \mathbf{Y}$$

$$\mathbf{C} = \overline{\left(\overline{(\mathbf{X} \cdot \mathbf{Y})}\right)}$$

These equations lead to several implementations.

#### **Five Implementations: Half-Adder**

- We can derive following sets of equations for a halfadder:

- (a)  $S = X \cdot \overline{Y} + \overline{X} \cdot Y$   $C = X \cdot Y$ (b)  $S = (X + Y) \cdot (\overline{X} + \overline{Y})$   $C = X \cdot Y$ (c)  $S = (C + \overline{X} \cdot \overline{Y})$   $C = X \cdot Y$ (d)  $S = (X + Y) \cdot \overline{C}$   $\overline{C} = (X + Y) \cdot \overline{C}$ (e)  $S = X \oplus Y$   $C = X \cdot Y$ (f)  $S = (C + \overline{X} \cdot \overline{Y})$  $C = X \cdot Y$

- (a), (b), and (e) are SOP, POS, and XOR implementations for S.

- In (c), the C function is used as a term in the AND-NOR implementation of S, and in (d), the C function is used in a POS term for S.

Logic and Computer Design Fundamentals PowerPoint® Slides © 2004 Pearson Education, Inc.

#### **Implementations: Half-Adder**

The most common half adder implementation is:

$$\mathbf{S} = \mathbf{X} \oplus \mathbf{Y}$$

$$\mathbf{C} = \mathbf{X} \cdot \mathbf{Y}$$

$$X \longrightarrow S (e)$$

• A NAND only implementation is:  $S = (X + Y) \cdot C$   $C = ((X \cdot Y))$   $X \rightarrow C$   $V \rightarrow C$  $V \rightarrow$

## **Functional Block: Full-Adder**

A full adder is similar to a half adder, but includes a carry-in bit from lower stages. Like the half-adder, it computes a sum bit, S and a carry bit, C.

| <ul> <li>For a carry-in (Z) of</li> </ul> | Z   | 0   | 0  | 0   | 0  |

|-------------------------------------------|-----|-----|----|-----|----|

| 0, it is the same as                      | X   | 0   | 0  | 1   | 1  |

| the half-adder:                           | + Y | + 0 | +1 | + 0 | +1 |

|                                           | C S | 00  | 01 | 01  | 10 |

| <ul> <li>For a carry- in</li> </ul>       |     |     |    |     |    |

| (Z) of 1:                                 | Z   | 1   | 1  | 1   | 1  |

|                                           | X   | 0   | 0  | 1   | 1  |

|                                           | + Y | +0  | +1 | + 0 | +1 |

|                                           | C S | 01  | 10 | 10  | 11 |

| onic and Computer Dealon Fondamentale     |     |     |    |     |    |

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Peerson Education, Inc.

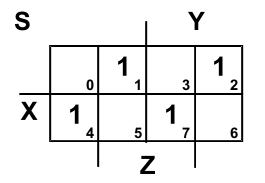

#### **Logic Optimization: Full-Adder**

| Full-Adder Truth Table: | X | Y | Z | С | S |

|-------------------------|---|---|---|---|---|

|                         | 0 | 0 | 0 | 0 | 0 |

|                         | 0 | 0 | 1 | 0 | 1 |

|                         | 0 | 1 | 0 | 0 | 1 |

|                         | 0 | 1 | 1 | 1 | 0 |

|                         | 1 | 0 | 0 | 0 | 1 |

|                         | 1 | 0 | 1 | 1 | 0 |

| Full-Adder K-Map:       | 1 | 1 | 0 | 1 | 0 |

| -                       | 1 | 1 | 1 | 1 | 1 |

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Pearson Education, Inc.

## **Equations: Full-Adder**

- From the K-Map, we get:

- $S = X \overline{Y} \overline{Z} + \overline{X} Y \overline{Z} + \overline{X} \overline{Y} \overline{Z} + X Y Z$ C = X Y + X Z + Y Z

- The S function is the three-bit XOR function (Odd Function):

$\mathbf{S} = \mathbf{X} \oplus \mathbf{Y} \oplus \mathbf{Z}$

The Carry bit C is 1 if both X and Y are 1 or if the sum is 1 and a carry-in (Z) occurs. Thus C can be rewritten as:

$\mathbf{C} = \mathbf{X} \mathbf{Y} + (\mathbf{X} \oplus \mathbf{Y}) \mathbf{Z}$

- The term X·Y is *carry generate*.

- The term X⊕Y is *carry propagate*. (why?)

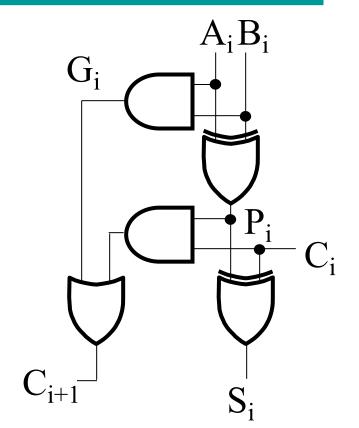

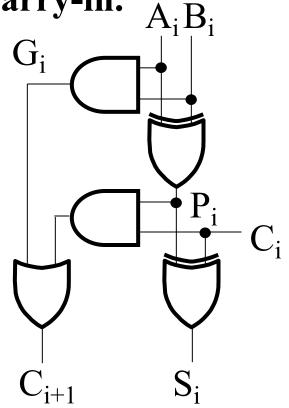

## **Implementation: Full Adder**

- Full Adder Schematic

- Here X, Y, and Z, and C (from the previous pages) are A, B, C<sub>i</sub> and C<sub>i+1</sub>, respectively. Also,

**G** = generate and

- **P** = propagate.

- Note: This is really a combination of a 3-bit odd function (for S)) and Carry logic (for C<sub>i+1</sub>):

(G = Generate) OR (P = Propagate AND C<sub>i</sub> = Carry In)

$$\mathbf{C}_{i+1} = \mathbf{G} + \mathbf{P}_i \cdot \mathbf{C}_i$$

Logic and Computer Dealgn Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Pearson Education, Inc.

### **Logic Diagram of Full Adder**

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Pearson Education, Inc.

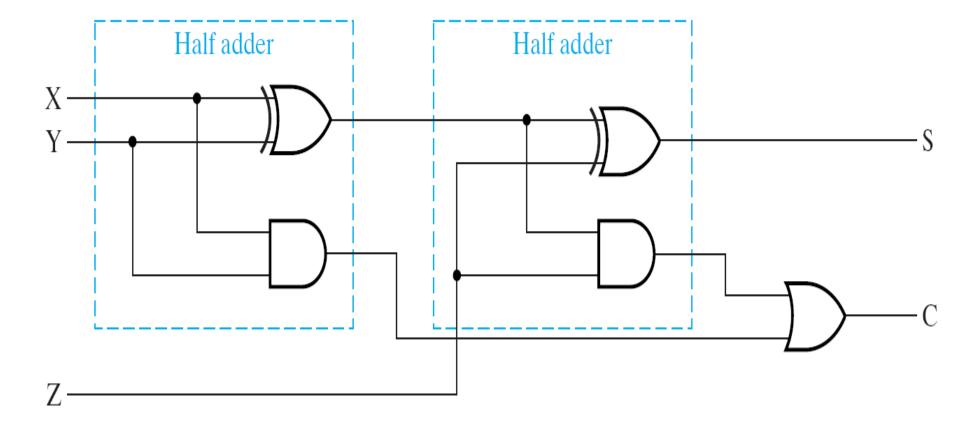

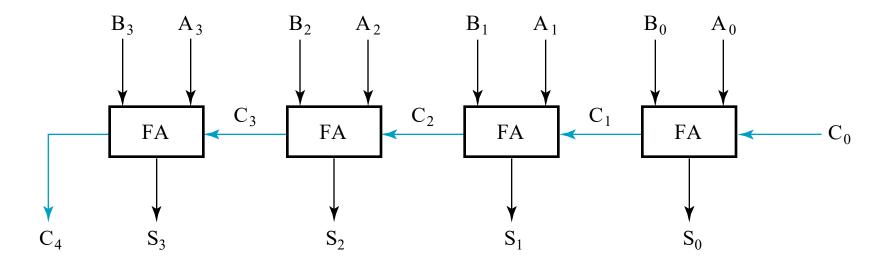

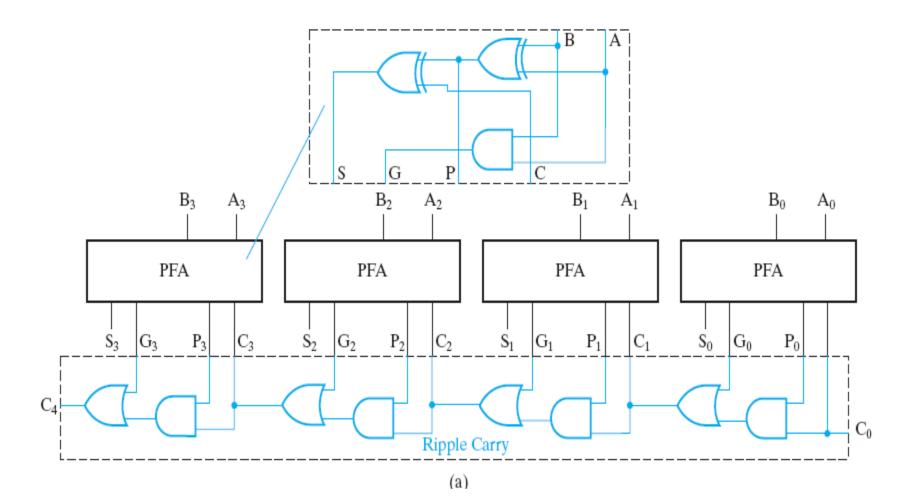

## **Binary Adders**

- To add multiple operands, we "bundle" logical signals together into vectors and use functional blocks that operate on the vectors

- Example: <u>4-bit ripple carry</u> <u>adder:</u> Adds input vectors

A(3:0) and B(3:0) to get a sum vector S(3:0)

- Note: carry out of cell i becomes carry in of cell i + 1

| Description | Subscript<br>3 2 1 0 | Name             |

|-------------|----------------------|------------------|

| Carry In    | 0110                 | C <sub>i</sub>   |

| Augend      | 1011                 | A <sub>i</sub>   |

| Addend      | 0011                 | B <sub>i</sub>   |

| Sum         | 1110                 | S <sub>i</sub>   |

| Carry out   | 0011                 | C <sub>i+1</sub> |

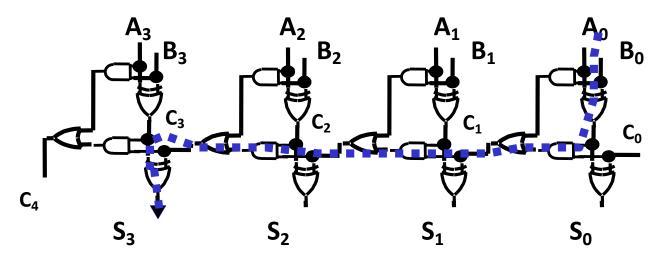

#### 4-bit Ripple-Carry Binary Adder

A four-bit Ripple Carry Adder made from four 1-bit Full Adders:

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Pearson Education, Inc.

## **Ripple Carry**

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Pearson Education, Inc.

Chapter 5 17

## **Carry Propagation & Delay**

- One problem with the addition of binary numbers is the length of time to propagate the ripple carry from the least significant bit to the most significant bit.

- The gate-level propagation path for a 4-bit ripple carry adder of the last example:

Note: The "long path" is from A<sub>0</sub> or B<sub>0</sub> though the circuit to S<sub>3</sub>.

Logic and Computer Design Fundamentals PowerPoint® Slides © 2004 Pearson Education, Inc.

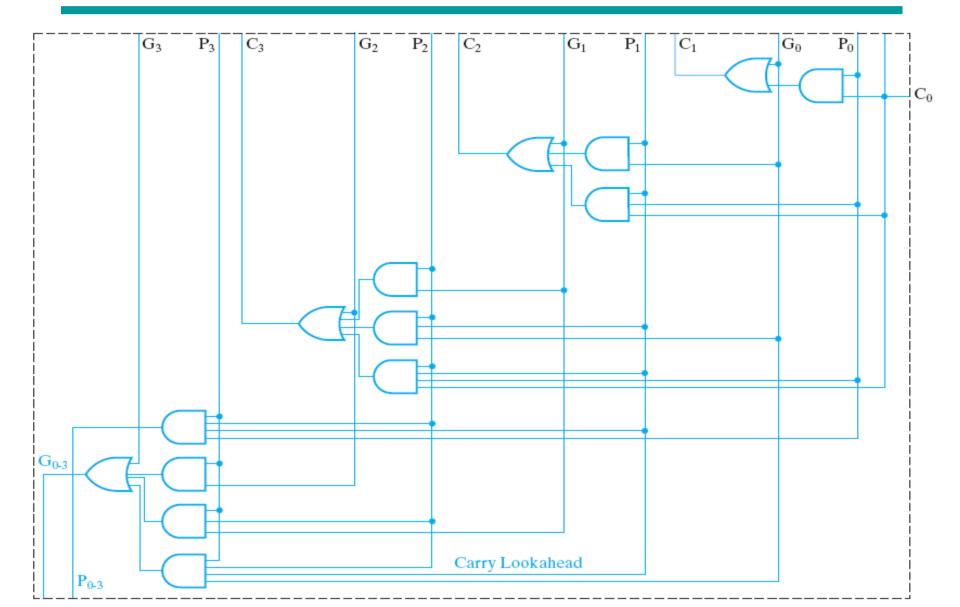

## **Carry Lookahead**

- Given Stage i from a Full Adder, we know that there will be a <u>carry generated</u> when A<sub>i</sub> = B<sub>i</sub> = "1", whether or not there is a carry-in. A.B.

- Alternately, there will be a <u>carry propagated</u> if the "half-sum" is "1" and a carry-in, C<sub>i</sub> occurs.

- These two signal conditions are called *generate*, denoted as G<sub>i</sub>, and *propagate*, denoted as P<sub>i</sub> respectively and are identified in the circuit:

#### Carry Lookahead (continued)

- In the ripple carry adder:

- Gi, Pi, and Si are <u>local</u> to each cell of the adder

- Ci is also local each cell

- In the carry lookahead adder, in order to reduce the length of the carry chain, Ci is changed to a more global function spanning multiple cells

- Defining the equations for the Full Adder in term of the P<sub>i</sub> and G<sub>i</sub>:

- $P_i = A_i \bigoplus B_i \qquad G_i = A_i B_i$  $S_i = P_i \bigoplus C_i \qquad C_{i+1} = G_i + P_i C_i$

#### **Carry Lookahead Development**

- C<sub>i+1</sub> can be removed from the cells and used to derive a set of carry equations spanning multiple cells.

- Beginning at the cell 0 with carry in C<sub>0</sub>:

$$\begin{split} C_1 &= G_0 + P_0 \ C_0 \\ C_2 &= G_1 + P_1 \ C_1 = \ G_1 + P_1 (G_0 + P_0 \ C_0) \\ &= G_1 + P_1 G_0 + P_1 P_0 \ C_0 \\ C_3 &= G_2 + P_2 \ C_2 = \ G_2 + P_2 (G_1 + P_1 G_0 + P_1 P_0 \ C_0) \\ &= G_2 + P_2 G_1 + P_2 P_1 G_0 + P_2 P_1 P_0 \ C_0 \\ C_4 &= G_3 + P_3 \ C_3 = G_3 + P_3 G_2 + P_3 P_2 G_1 \\ &+ P_3 P_2 P_1 G_0 + P_3 P_2 P_1 P_0 \ C_0 \end{split}$$

Logic and Computer Design Fundamenta PowerPoint<sup>®</sup> Slides © 2004 Pearson Education, Inc.

#### **Carry Lookahead Adder**